## onsemi

# MOSFET Selection for Reverse Polarity Protection AND90146/D

#### OVERVIEW

When the vehicle's battery is damaged and needs replacement the probability of connecting the new battery in reverse is high. Since many electronic control units (ECU) in the vehicle are connected to the vehicle's battery, such an event could lead to numerous ECU failures. Additionally, automotive standards like ISO (International Organization for Standardization) defines the testing methods, voltage levels, limits for electromagnetic emission for electrical and electronic devices to ensure the safe and rugged operation of the system. One such standard related to reverse polarity protection (RPP) is ISO 7637-2:2011 which replicates the various voltage scenarios like in the real application and the system needs to withstand such voltages to showcase the robustness against failures. This made reverse polarity protection a crucial building block that is required by all automotive vehicle manufacturers for any battery connected ECU/system.

This application note will first address the ISO pulses that are commonly used to replicate the voltage transients that could appear in real applications. It will then give details about several protection techniques that could be used, before helping to guide the reader to select an external N–Channel MOSFET, that will provide RPP and help reduce the power losses of the system. Finally, a list of recommended N–Channel MOSFETs to be used along with an ideal diode controller, based on the battery current will be provided.

#### **ISO PULSES**

ISO 7637–2:2011 is an international standard which specifies test methods and procedures to ensure the compatibility to conducted electrical transients of equipment installed on passenger cars and commercial vehicles fitted with 12 V or 24 V electrical systems. Refer to ISO 7637–2:2011 for detailed information.

Under this standard there are several types of test pulses that are defined to test the device. Below are few of the test pulses.

- Pulse 1: Transients due to supply disconnection of inductive loads.

- Pulse 2a: Transients due to sudden interruption of currents in a device connected in parallel with the DUT (Device Under Test), due to the inductance of the wiring harness.

- Pulse 3a & 3b: Transients which occur as a result of switching processes. The characteristics of these transients are influenced by distributed capacitance and inductance of the wiring harness.

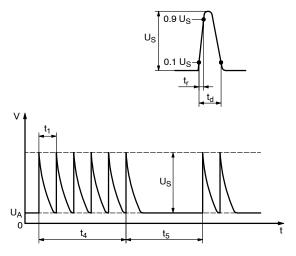

These test pulses come with different negative and positive voltage levels to stress the DUT to see if it can withstand. For example, Pulse 3b is shown in Figure 1 to give an idea about the type of pulses that are defined in the standard, each pulse will have its own parameters as in Table 1. Pulse 3b simulates the switching noise in the real application, such as relay and switch contact bouncing which can produce a short burst of high frequency pulses. <u>AND8228/D</u> talks in more details about voltage transients and testing methods.

Figure 1. Test Pulse 3b

Table 1. PARAMETERS OF TEST PULSE 3b

| Parameters     | Nominal 12 V System | Nominal 24 V System |  |  |  |  |  |

|----------------|---------------------|---------------------|--|--|--|--|--|

| U <sub>S</sub> | +75 V to +150 V     | +150 V to +300 V    |  |  |  |  |  |

| R <sub>i</sub> | 50                  | Ω                   |  |  |  |  |  |

| t <sub>d</sub> | 150 ns ±45 ns       |                     |  |  |  |  |  |

| t <sub>r</sub> | 5 ns ±1.5 ns        |                     |  |  |  |  |  |

| t <sub>1</sub> | 100 μs              |                     |  |  |  |  |  |

| t <sub>4</sub> | 10 ms               |                     |  |  |  |  |  |

| t <sub>5</sub> | 90 ms               |                     |  |  |  |  |  |

#### REVERSE POLARITY PROTECTION TECHNIQUES

In the following section the three most common techniques used for reverse polarity protection are discussed.

#### Diode

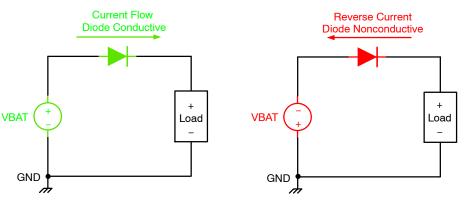

The simplest way to protect a system from a reverse battery is by using a diode. As shown in Figure 2, a diode will

Figure 2. Reverse Polarity Protection using a Diode

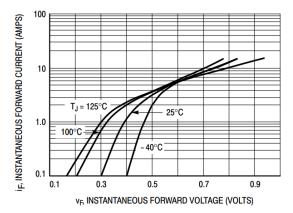

Figure 3 shows the typical voltage drop of the <u>NRVBSS24NT3G Schottky diode</u>. If the diode current  $(I_{DIODE})$  increases from 0.5 A to 1.0 A (100% increase), V<sub>F</sub>

increases from 0.35 V to 0.40 V (15% increase) at a junction temperature  $T_J$  of 25°C.

Figure 3. Typical Forward Voltage of NRVBSS24NT3G Schottky Diode

#### MOSFET

An alternative to a diode is a MOSFET. When a MOSFET is conductive, the voltage drop between the drain–source  $V_{DS}$  is dependent on the drain–source resistance  $R_{DS,ON}$  and the drain–source current  $I_D$ :  $V_{DS} = R_{DS,ON} * I_D$ . Compared to a Schottky diode the voltage drop is generally much lower.

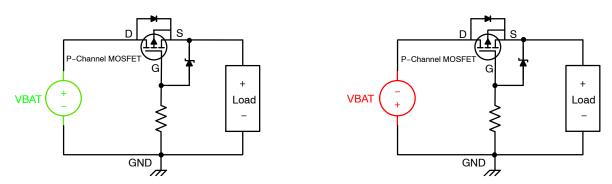

#### P-Channel MOSFET

As all MOSFETs, a P-Channel MOSFET has an intrinsic body diode between the source and the drain. When the

battery is properly connected, the intrinsic body diode is conductive till the MOSFET's channel is turned ON. To turn ON a P–Channel MOSFET, the gate voltage needs to be lower than the source voltage by at least the threshold voltage  $V_T$ . When the battery is reversely connected, the body diode is reversed biased, gate and source have the same voltage thus turning OFF the P–Channel MOSFET. An additional Zener diode is used to clamp the gate of the P–Channel MOSFET and protect it in the case of a too high voltage.

only conduct current when the correct polarity is applied to its terminals (i.e., forward biased). The forward voltage drop,  $V_F$  for a standard diode is around 0.7 V, while for a Schottky diode it can be as low as 0.3 V. As a result, most applications use a Schottky diode, to reduce system losses.

Figure 4. Reverse Polarity Protection using a P-Channel MOSFET

#### N-Channel MOSFET

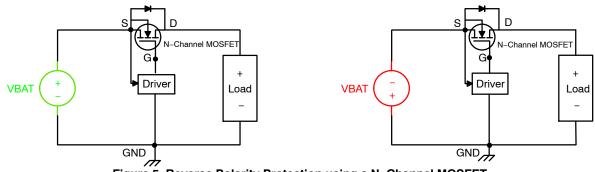

It is also possible to use an N–Channel MOSFET for reverse polarity protection. When the battery is properly connected (source is connected to  $V_{BAT}$ ), to turn ON the MOSFET, the gate–source voltage has to be higher than the threshold voltage ( $V_{GS} > V_{TH}$ ). Given that the source is connected to  $V_{BAT}$ , the gate voltage needs to be higher than  $V_{BAT}$  by at least  $V_T$ . Hence a dedicated driver is used to drive the gate voltage of the N–Channel MOSFET higher than the source voltage, thus turning ON the N–Channel MOSFET. When the battery is reverse connected, the body diode is reversed biased (anode voltage is lower than cathode voltage) and the driver is disabled (source and gate are shorted), turning the N–Channel MOSFET OFF.

Figure 5. Reverse Polarity Protection using a N-Channel MOSFET

#### Comparison of Reverse Polarity Protection Techniques

Table 2 summarizes the advantages and disadvantages of the different reverse polarity protection techniques. It is worth mentioning that P–Channel MOSFET operation depends upon the mobility of holes, while an N–Channel MOSFET depends upon the mobility of electrons. Knowing that the mobility of holes is almost 2.5 times lower than the mobility of electrons, for the same drain current, a P–Channel MOSFET will have a bigger die size and, by implication, a higher cost compared to that of an N–Channel MOSFET to achieve the same on–resistance. This makes N–Channel MOSFETs preferable compared to P–Channel MOSFETs in such applications.

### Table 2. COMPARISON BETWEEN DIFFERENT PROTECTION TECHNIQUES

|                   | Advantages                                                                                                                                               | Disadvantages                                                                                                                                                                                                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Schottky<br>Diode | <ul><li>Low cost</li><li>Simple</li></ul>                                                                                                                | <ul> <li>Higher power<br/>dissipation</li> <li>Higher voltage drop</li> </ul>                                                                                                                                          |

| MOSFET            | <ul> <li>Flexibility (various MOSFETs with various R<sub>DS,ON</sub>)</li> <li>Higher power dissipation</li> <li>Lower operating voltage drop</li> </ul> | <ul> <li>High cost for low R<sub>DS,ON</sub></li> <li>Higher total solution cost<br/>(need of additional<br/>charge pump / controller)</li> <li>Higher complexity<br/>(i.e., gate drive and<br/>protection)</li> </ul> |

#### **MOSFET SELECTION**

There are various parameters to consider when selecting an N–Channel MOSFET for reverse polarity protection.

- Maximum Breakdown Voltage of the MOSFET V<sub>DS.MAX</sub>

- For 12 V board net (vehicle) V<sub>DS,MAX</sub> = 40 V is preferred

- For 24 V board net (truck) V<sub>DS,MAX</sub> = 60V is preferred

- Maximum Operating Junction Temperature T<sub>J,MAX</sub>

- For vehicle and truck applications, 175°C is recommended given the harsh environment

- Gate Level

- Logic Level is preferred over standard level since they have a lower R<sub>DS,ON</sub> for the same gate-source voltage V<sub>GS</sub>

- Package

- ◆ 3.30 × 3.30 mm (i.e. LFPAK33/WDFN8/µ8FL) and 5.00 × 6.00 mm (i.e., SO8-FL/LFPAK56) packages with exposed pad for optimized power dissipation are commonly used

- Total Gate Charge Q<sub>G,TOT</sub>

- Turning ON a MOSFET happens in 3 phases

- When the gate voltage  $V_{GS}$  rises to the plateau voltage  $V_{GP}$ , charges are mainly used to charge the input capacitance  $C_{ISS}$ .

- When V<sub>GS</sub> is at the plateau voltage V<sub>GB</sub> charges are mainly used to charge the reverse transfer capacitance (gate-to-drain capacitance) C<sub>RSS</sub>.

- When V<sub>GS</sub> rises from V<sub>GP</sub> to driver supply voltage V<sub>GDR</sub>, the charges are used to further enhance the channel.

- Lower the Q<sub>G,TOT</sub>, lesser the gate voltage and current needed to turn ON the MOSFET (i.e., faster turn ON) and vice versa

- More information about MOSFET Gate-Charge could be found in the following **onsemi** application note.

- <u>https://www.onsemi.com/pub/Collateral/</u> <u>AND9083–D.PDF</u>

- Drain–Source Resistance R<sub>DS,ON</sub>

- R<sub>DS,ON</sub> plays a role to limit the power dissipation in the device. The higher the R<sub>DS,ON</sub> for a given load current, the higher is the power dissipation. Higher losses lead to the increase in T<sub>J</sub> of the MOSFET. Hence it is important to choose the right device with required R<sub>DS,ON</sub> to have optimal performance.

- In the following sections, MOSFETs for thermal evaluation are chosen in such a way that their R<sub>DS,ON</sub> will keep power dissipation around 500 mW of losses.

#### NCV68061 IDEAL DIODE CONTROLLER

The combination of NCV68061 and an external N–Channel MOSFET replicates an ideal diode which acts like a perfect conductor when forward biased voltage (anode voltage is higher than cathode) is applied and like a perfect insulator when the reverse biased voltage (anode voltage is lower than cathode) is applied. The NCV68061 is a reverse polarity protection and ideal diode N–Channel MOSFET controller intended as a lower loss and lower forward voltage replacement for diodes.

The main function of the NCV68061 is to control the ON/OFF state of an external N–Channel MOSFET according to the source to drain differential voltage polarity. Depending on the drain pin connection the device can be configured in two different application modes. With the drain pin is connected to the load the application is in ideal diode mode, whereas with the drain pin connected to ground the NCV68061 is merely in reverse polarity protection mode. In both modes, the controller provides a typical gate voltage of 11.4 V to external N–Channel MOSFET. Hence in all the calculations of following sections,  $R_{DS,ON}$  @ 10 V  $V_{GS}$  has been used.

NCV68061 has undergone ISO 7637–2:2011 tests to demonstrate the robustness of the device to withstand voltage stress. The results are shown in the <u>NCV68061</u> datasheet.

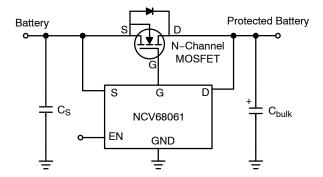

#### **Ideal Diode Application**

Figure 6 shows how the NCV68061 is used in the ideal diode configuration. In this configuration, the input voltage is not allowed to discharge the bulk capacitance  $C_{bulk}$ . This configuration has two modes:

- Conduction Mode: Prior to entering the conduction mode, the source voltage is lower than the drain voltage, and both the charge pump and the N-Channel MOSFET are disabled. As the source voltage becomes greater than the drain voltage, the forward current flows through the body diode of the N-Channel MOSFET. Once this forward voltage drop exceeds the source to drain gate charge voltage threshold level (typ. 140 mV), the charge pump is turned ON and the N-Channel MOSFET becomes fully conductive.

- Reverse Current Blocking Mode: When the source voltage becomes less than the drain voltage, reverse current initially flows through the conductive channel of the N-Channel MOSFET. This current creates a voltage drop across the conductive channel of the N-Channel MOSFET which is proportional to its R<sub>DS,ON</sub>. When this voltage drops below the source to drain gate discharge voltage threshold (typ. -10 mV), the charge pump is disabled, and the external N-Channel MOSFET of the controller.

Figure 6. NCV68061 Ideal Diode Application

#### **Reverse Polarity Protection**

By connecting the drain pin to the GND potential, as shown in Figure 7, the NCV68061 does not allow a falling input voltage to discharge the output below GND potential but does allow the output to follow any positive input voltage above the under-voltage lockout (UVLO) threshold. This means that the bulk capacitance  $C_{bulk}$  will be discharged by a falling input voltage.

When the source voltage is above the UVLO threshold (typ. 3.3 V), the source/drain and UVLO comparators enable the charge pump to provide gate-source voltage to the external N-Channel MOSFET, which is fully conductive. When the source voltage is below the UVLO threshold (typ. 3.2 V), the charge pump and the N-Channel MOSFET are disabled, and any load current flows through the body diode of the N-Channel MOSFET.

Figure 7. NCV68061 Reverse Polarity Protection Application

#### **TEST SETUP**

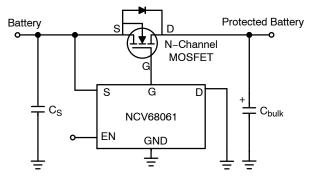

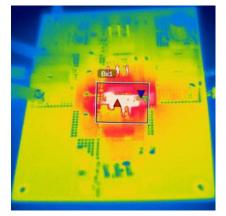

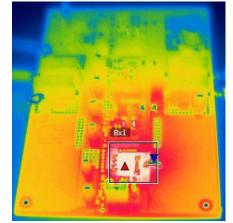

A dedicated test board for NCV68061 is used to determine the power dissipation and thermal performance of the various MOSFETs in  $3 \times 3$  and  $5 \times 6$  packages with different  $R_{DS,ON}$  to help to understand the MOSFET selection for the ideal diode controller considering various load currents.

#### Schematic

Figure 8 shows the schematic of the test board. It is designed in such a way that MOSFETs in SO-8FL/LFPAK4 and  $\mu$ 8FL/LFPAK33 can be tested. Each MOSFET circuit has a jumper to enable/disable the NCV68061 to make sure that only one controller is active at a time. A 3.3 V LDO NCV4294 is used to supply the enable pin EN of the controller. The controller will control the N-Channel MOSFET to act like an ideal diode and also to block reverse current.

Figure 8. Schematic of NCV68061 Test Board

#### Layout

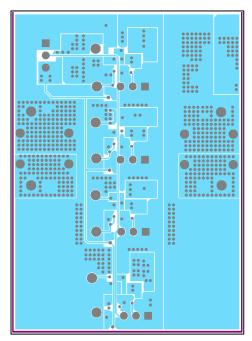

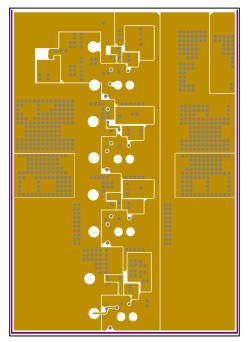

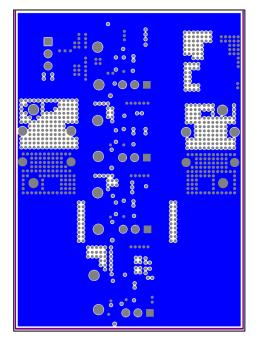

The board is a 4-layer printed circuit board (PCB). The input and output currents have been distributed across top, inner1 and inner2 layers. Distributing the current across

Figure 9. Top Layer

Figure 11. Inner2 Layer

several layers helps to reduce the losses and to have better thermal performance of the board. Inner2 layer has traces for gate signals and for enable signal. Bottom layer is fully dedicated for the GND plane.

Figure 10. Inner1 Layer

Figure 12. Bottom Layer

#### THERMAL MEASUREMENTS

| Battery<br>Current | Part Number       | Package | Maximum R <sub>DS,ON</sub> @ 10 V<br>V <sub>GS</sub> (mΩ) | Maximum Losses<br>P <sub>D</sub> (mW) | R <sub>θJA</sub> (°C/W) | T <sub>CASE</sub> (°C) |

|--------------------|-------------------|---------|-----------------------------------------------------------|---------------------------------------|-------------------------|------------------------|

| 6 A                | NVTFS5C478NLWFTAG | μ8FL    | 14.0                                                      | 504.0                                 | 51.0                    | 47.3                   |

|                    | NVMFS5C468NLAFT1G | SO-8FL  | 10.3                                                      | 370.8                                 | 43.0                    | 40.1                   |

| 8 A                | NVTFS5C466NLWFTAG | μ8FL    | 7.3                                                       | 467.2                                 | 48.0                    | 47.4                   |

|                    | NVMFS5C466NLWFT1G | SO-8FL  | 7.3                                                       | 467.2                                 | 43.0                    | 45.3                   |

| 10 A               | NVTYS005N04CLTWG  | LFPAK8  | 4.8                                                       | 480.0                                 | 47.7                    | 52.8                   |

|                    | NVMYS4D6N04CLTWG  | LFPAK4  | 4.5                                                       | 450.0                                 | 40.0                    | 47.5                   |

#### Table 3. MOSFETS UNDER EVALUATION

Table 3 shows the N–Channel MOSFETs used for thermal evaluation. MOSFETs with various  $R_{DS,ON}$  are chosen to limit the power dissipation to be around 500 mW. Measurements of the MOSFETs top case temperature are made at 24°C ambient temperature to evaluate the thermal

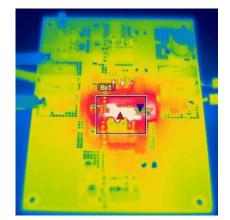

Figure 13. 6 A with  $\mu$ 8FL

| Part Number                              | NVTFS5C478NLWFTAG |  |  |  |

|------------------------------------------|-------------------|--|--|--|

| Max. $R_{DS(ON)}$ @ 10 V V <sub>GS</sub> | 14.0 m $\Omega$   |  |  |  |

| Max. Temperature                         | 47.3°C            |  |  |  |

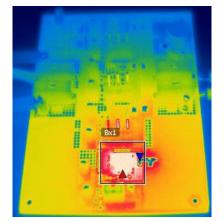

#### Figure 15. 8 A with $\mu$ 8FL

| Part Number                                     | NVTFS5C466NLWFTAG |

|-------------------------------------------------|-------------------|

| Max. R <sub>DS(ON)</sub> @ 10 V V <sub>GS</sub> | 7.3 mΩ            |

| Max. Temperature                                | 47.4°C            |

performance of the MOSFETs with different output currents (6 A, 8 A and 10 A). MOSFETs in SO–8FL/LFPAK4 (5 x 6) and  $\mu$ 8FL/LFPAK8 (3 × 3) are used for evaluation. Two measurements are made for each load current, one with 5 x 6 and another with 3 × 3 package.

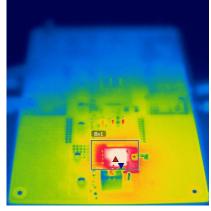

Figure 14. 6 A with SO-8FL

| Part Number                               | NVMFS5C468NLAFT1G |  |  |  |

|-------------------------------------------|-------------------|--|--|--|

| Max. $\rm R_{DS(ON)}$ @ 10 V $\rm V_{GS}$ | 10.3 m $\Omega$   |  |  |  |

| Max. Temperature                          | 40.1°C            |  |  |  |

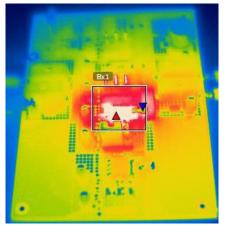

Figure 16. 8 A with SO-8FL

| Part Number                                     | NVMFS5C466NLWFT1G |

|-------------------------------------------------|-------------------|

| Max. R <sub>DS(ON)</sub> @ 10 V V <sub>GS</sub> | 7.3 mΩ            |

| Max. Temperature                                | 45.3°C            |

Figure 17. 10 A with LFPAK8

| Part Number                                     | NVTYS005N04CLTWG |

|-------------------------------------------------|------------------|

| Max. R <sub>DS(ON)</sub> @ 10 V V <sub>GS</sub> | 4.8 mΩ           |

| Max. Temperature                                | 52.8°C           |

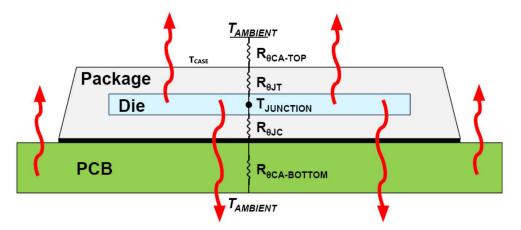

With the measured top case temperature from thermal measurements and calculated power dissipation, the junction temperature  $T_J$  can be calculated using equation 1.

$$T_{J} = T_{CASE} + P_{D} \times R_{\theta JT}$$

(eq. 1)

Figure 18. 10 A with LFPAK4

| Part Number                              | NVMYS4D6N04CLTWG       |

|------------------------------------------|------------------------|

| Max. $R_{DS(ON)}$ @ 10 V V <sub>GS</sub> | $4.5~\mathrm{m}\Omega$ |

| Max. Temperature                         | 45.3°C                 |

- T<sub>J</sub> = Junction temperature of the MOSFET

- $T_{CASE}$  = Temperature of the package on top measured by the thermal camera

P<sub>D</sub> = Power dissipation of the MOSFET

$R_{\theta JT}$  = Thermal resistance between top case and junction of the MOSFET

Figure 19. Equivalent Thermal Resistance of the MOSFET

The value of  $R_{\theta JT}$  is not fixed, it depends on thermal boundary conditions such as PCB layout, cooling system of the MOSFET (like exposed pad) and other parameters, therefore it is not provided in the datasheet.  $R_{\theta JT}$  is a small number with < 1°C/W, as most of the heat will flow from junction to the PCB via the exposed pad on the bottom side of the package. Therefore, not much heat flows from the junction to the top of the MOSFET and one can assume that the temperature difference between  $T_J$  and  $T_{CASE}$  is not significant. For the sake of the application note, the assumption is that  $R_{\theta JT}$  is 1°C/W to determine  $T_J.$

NOTE:  $1^{\circ}C/W$  is a very conservative assumption for  $3 \times 3$  and  $5 \times 6$  packages. Other packages will have a different thermal resistance.

#### Estimation of the Junction Temperature ${\sf T}_{\sf J}$

In the following section, the measured  $T_{CASE}$  and actual power dissipation in the MOSFET are used to calculate  $T_J$ . In the next step a theoretical calculation based on specifications of the datasheets is done and the result is compared to the calculations made using measured data to see if both theoretical and practical calculations of  $T_J$  are matching. All calculations consider MOSFET NVTFS5C478NLWFTAG in  $\mu$ 8FL (3 × 3) package.

#### Estimation for T<sub>J</sub> Using Measured T<sub>CASE</sub>

The below calculations are done to estimate  $T_J$  using values obtained from measurements.

- Load current  $I_{LOAD} = I_D = 6.0 \text{ A}$

- Input voltage  $V_{in} = 12.0 V$

- Temperature of top case  $T_{CASE} = 47.3$  °C (obtained from the thermal measurement)

- Max. on-resistance  $R_{DS,ON}$  @ 10.0 V V<sub>GS</sub> = 14.0 m $\Omega$

- $R_{\theta JT} = 1.0^{\circ}C/W$  (assumption for  $3 \times 3$  and  $5 \times 6$  packages)

$$\mathsf{P}_{\mathsf{D}} = \mathsf{I}_{\mathsf{D}}^2 \times \mathsf{R}_{\mathsf{DS},\,\mathsf{ON}}$$

$$P_{D} = (6.0 \text{ A})^{2} \times 14.0 \text{ m}\Omega = 504.0 \text{ mW}$$

(eq. 2)

Using Equation 1,

$$T_{\rm J} = 47.3^{\circ}C + (504.0 \text{ mW} \times 1.0^{\circ}C/W) = 47.8^{\circ}C$$

#### Theoretical Calculation for $T_J$

Theoretical calculations based on specification of the datasheet are used to determine  $T_J$ . Assuming losses of 500 mW, the equation 3 is used to determine  $T_J$  of the device.

$$\mathsf{P}_{\mathsf{D}} = \frac{\mathsf{T}_{\mathsf{J}} - \mathsf{T}_{\mathsf{A}}}{\mathsf{R}_{\theta\mathsf{J}\mathsf{A}}} \tag{eq. 3}$$

- Junction temperature of the MOSFET T<sub>J</sub>

- Ambient temperature at which the MOSFET will be operated  $T_A = 24.0^{\circ}C$

- Power dissipation of the MOSFET  $P_D = 500.0 \text{ mW}$

- Thermal resistance between junction and ambient of the MOSFET  $R_{\theta JA} = 51.0^{\circ}C/W$  (value from the datasheet)

$$T_J = P_D \times R_{\theta JA} + T_A$$

= 500.0 mW  $\times$  51.0°C/W + 24.0°C = 49.5°C (eq. 4)

This gives 125.5°C headroom for  $T_{J,MAX}$  of 175.0°C for <u>NVTFS5C478NLWFTAG</u>.

The difference between estimated and theoretically calculated  $T_J$ 's is minor at 1.7°C (49.5°C vs. 47.8°C). In Table 4, as shown in the above calculations, theoretically calculated  $T_J$  and measured  $T_{CASE}$ ,  $R_{\theta JT}$  and  $P_D$  are used to estimate  $T_J$  for various loads and packages.

|                    |                   |                               |                                                      |                                          |      | R <sub>θJA</sub> Measured |                                                        | T <sub>J</sub> (°C)                |                                                                     | Estimated T <sub>J</sub>                                              |

|--------------------|-------------------|-------------------------------|------------------------------------------------------|------------------------------------------|------|---------------------------|--------------------------------------------------------|------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|

| Battery<br>Current | Part Number       | R <sub>DS, ON</sub><br>10 V V | Maximum<br>R <sub>DS, ON</sub> @<br>10 V VGS<br>(mΩ) | Maximum<br>Losses P <sub>D</sub><br>(mW) |      |                           | Estimated @<br>24°C Ambient<br>Based on<br>Measurement | Calculated<br>Theoretical<br>Value | ΔT <sub>J</sub><br>Between<br>Theoretical<br>and Scaled<br>Up Value | Headroom<br>from Maximum<br>175 °C<br>Based on<br>Measurement<br>(°C) |

| 6 A                | NVTFS5C478NLWFTAG | μ8FL                          | 14.0                                                 | 504.0                                    | 51.0 | 47.3                      | 47.8                                                   | 49.5                               | -1.7                                                                | 127.2                                                                 |

|                    | NVMFS5C468NLAFT1G | SO-8FL                        | 10.3                                                 | 370.8                                    | 43.0 | 40.1                      | 40.4                                                   | 45.5                               | -5.1                                                                | 134.6                                                                 |

| 8 A                | NVTFS5C466NLWFTAG | μ8FL                          | 7.3                                                  | 467.2                                    | 48.0 | 47.4                      | 47.8                                                   | 48.0                               | +0.2                                                                | 127.2                                                                 |

|                    | NVMFS5C466NLWFT1G | SO-8FL                        | 7.3                                                  | 467.2                                    | 43.0 | 45.3                      | 45.7                                                   | 45.5                               | +0.2                                                                | 129.3                                                                 |

| 10 A               | NVTYS005N04CLTWG  | LFPAK8                        | 4.8                                                  | 480.0                                    | 47.7 | 52.8                      | 53.2                                                   | 47.8                               | +5.4                                                                | 121.8                                                                 |

|                    | NVMYS4D6N04CLTWG  | LFPAK4                        | 4.5                                                  | 450.0                                    | 40.0 | 47.5                      | 47.9                                                   | 44.0                               | +3.9                                                                | 127.1                                                                 |

#### Table 4. CALCULATED T<sub>J</sub> OF THE PROPOSED MOSFETS VS. LOAD CURRENT

- At 6 A load current there is approximately 5.8 % higher head room for  $T_J$  with  $5 \times 6$  than  $3 \times 3$  package.

- At 8 A load, approximately 1.6 % higher head room with  $5 \times 6$  than  $3 \times 3$ . Both the devices are having the same die in different packages, therefore there is not much difference between T<sub>J</sub>'s is seen.

- At 10 A, approximately 4.3 % higher head room with 5 x 6 than with  $3 \times 3$ .

- Likewise, the difference in theoretical and estimated  $T_J$  is not significant except around 5.4°C difference for one of the 10 A MOSFETs. This shows that the  $R_{\theta JA}$  in the datasheet is reliable for this specific test setup.

- Measurement of  $R_{\theta JA}$  in the datasheet using 2 oz. copper pad with larger area board seems unrealistic from real application point of view but looking at the minor difference in  $T_J$  as estimated above shows that  $R_{\theta JA}$ matched quite well with 4-layer test board optimized for thermal dissipation.

- The results show that due to the larger package (5 × 6) the heat is getting dissipated efficiently and being distributed across the whole device hence there is better head room. Larger packaged devices are suitable for higher load current application from thermal point of view as well as for applications with higher ambient temperature.

#### Estimation of the Maximum Ambient Temperature T<sub>A</sub>

The previous calculations show that  $R_{\theta JA}$  of the datasheet matches quite well with the NCV68061 test board. Therefore, the maximum ambient temperature above which the MOSFET cannot not be operated can be calculated.

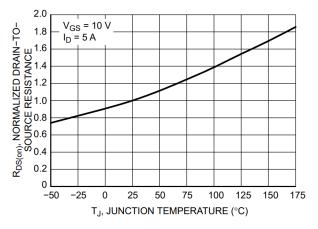

Figure 20 shows the variation of  $R_{DS,ON}$  in relation to  $T_J$  for NVTFS5C478NLWFTAG. At 175°C junction temperature, the maximum  $R_{DS,ON}$  is around 1.85 times higher compared to 25°C junction temperature. This results in a maximum  $R_{DS,ON}$  of  $1.85 \times 14 \text{ m}\Omega = -25.9 \text{ m}\Omega$ .

Figure 20. NVTFS5C478NLWFTAG On-Resistance Variation with Temperature

| Battery<br>Current | Part Number       | Package | Maximum R <sub>DS,ON</sub> @ 10 V<br>V <sub>GS</sub> @ 175°C Τ <sub>J</sub> (mΩ) | Maximum Losses<br>P <sub>D</sub> (mW) | R <sub>θJA</sub> (°C/W) | Estimated<br>Maximum<br>T <sub>AMB</sub> (°C) |

|--------------------|-------------------|---------|----------------------------------------------------------------------------------|---------------------------------------|-------------------------|-----------------------------------------------|

| 6 A                | NVTFS5C478NLWFTAG | μ8FL    | 25.9                                                                             | 932.4                                 | 51.0                    | 127.5                                         |

|                    | NVMFS5C468NLAFT1G | SO-8FL  | 19.6                                                                             | 705.6                                 | 43.0                    | 144.6                                         |

| 8 A                | NVTFS5C466NLWFTAG | μ8FL    | 14.4                                                                             | 921.6                                 | 48.0                    | 130.7                                         |

|                    | NVMFS5C466NLWFT1G | SO-8FL  | 13.2                                                                             | 844.8                                 | 43.0                    | 138.6                                         |

| 10 A               | NVTYS005N04CLTWG  | LFPAK8  | 8.8                                                                              | 880.0                                 | 47.7                    | 133.0                                         |

|                    | NVMYS4D6N04CLTWG  | LFPAK4  | 8.3                                                                              | 830.0                                 | 40.0                    | 141.8                                         |

Table 5. ESTIMATED MAXIMUM TAMB

The power dissipation at 175°C junction temperature and 6 A load current is as follows:

$$\textbf{P}_{D}\,=\,\left(\textbf{6.0 A}\right)^{2}\,\times\,\textbf{25.9 m}\Omega\,=\,\textbf{932.4 mW}$$

With  $R_{\theta JA} = 51.0^{\circ}C/W$ , the temperature difference between junction and ambient can be calculated:

Temperature difference  $\Delta T = 51.0^{\circ}C/W \times 932.4 \text{ mW} = 47.5^{\circ}C$

Maximum

$$T_A = T_J - \Delta T$$

Maximum

$$T_A = 175.0^{\circ}C - 47.5^{\circ}C = 127.5^{\circ}C$$

(eq. 5)

From the above example, the MOSFET can be operated at maximum ambient temperature of 127.5°C. If the ambient temperature goes above the calculated value, then it would mean that the  $T_J$  has reached over 175°C.

The silicon of the MOSFET itself can be operated at above  $175^{\circ}$ C, but due to the limitation of package mold compound and to ensure reliability over long-term operation, the MOSFET datasheet states that maximum T<sub>J</sub> to be  $175^{\circ}$ C. Temperature above maximum T<sub>J</sub> would lead to unguaranteed behavior of the device, and it also means that device is operating out of specification.

Table 5 shows the estimated maximum ambient temperature for various MOSFETS, considering different load currents and a junction temperature of 175°C.

#### CONCLUSION

Reverse polarity protection circuits are one of the core building blocks of any ECU in a vehicle. In this application note several reverse polarity protection techniques are discussed including diodes, P–Channel MOSFET and N–Channel MOFET. A comparison between all the techniques is presented highlighting advantages and disadvantages of each technique. Moreover, a MOSFET selection guide is given to support the MOSFET selection process, including a list of recommended devices. Thermal measurements with load currents from 6 A to 10 A show that  $5 \times 6$  packages perform well from thermal point of view, due to the larger package and bigger die, R<sub>DS,ON</sub> will be reduced and power losses are lesser than  $3 \times 3$  package. Additionally, a larger die helps to dissipate the heat better than with a smaller die. With that said, table 3 shows that the difference in margin for maximum  $T_J$  between  $5 \times 6$  and  $3 \times 3$  is not significant. Depending upon the application needs and cooling system used either  $5 \times 6$  or  $3 \times 3$  packaged MOSFETs can be used.

Without significant difference between the theoretically calculated and practically estimated junction temperature T<sub>J</sub>, R<sub>0JA</sub> given in the datasheet is a realistic value to perform thermal analysis in the real applications. R<sub>0JA</sub> helps to calculate the maximum ambient temperature at which the MOSFET can be operated using the calculations shown in the document earlier.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 **Europe, Middle East and Africa Technical Support:** Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative