#### **Document information**

| Information | Content                                                                                                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | GaN FET, parameters, data sheet                                                                                                              |

| Abstract    | This appplication note explains the content of Nexperia Power GaN FET data sheets.<br>Nomenclature, pinning and key parameters are detailed. |

## 1. Introduction

This application note examines in detail the data sheet for the GAN063-650WSA GaN FET device from Nexperia. Visit the product information page on Nexperia.com to download the latest version of the full data sheet.

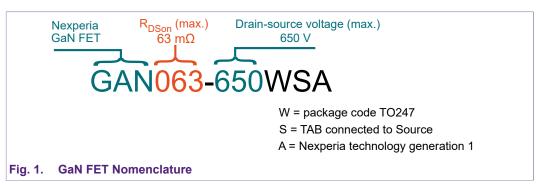

## 2. Nomenclature

The device name (type number) is shown at the top of the data sheet. The name contains some important information about the device. In the below example for GAN063-650WSA, the maximum on-state resistance and the limiting drain-source voltage are specified, together with letter codes indicating the package, the mounting base electrical connection and the technology generation.

## 3. Pinning information

#### Table 1. Pinning information

| Pin | Symbol | Description                        | Simplified outline                                          | Graphic symbol |

|-----|--------|------------------------------------|-------------------------------------------------------------|----------------|

| 1   | G      | gate                               | mb                                                          | D              |

| 2   | S      | source                             |                                                             |                |

| 3   | D      | drain                              | [°°°]                                                       |                |

| mb  | S      | mounting base; connected to source |                                                             | G_⊥IĘA         |

|     |        |                                    | $ \begin{bmatrix}     U & U \\                            $ | s              |

|     |        |                                    | TO-247 (SOT429)                                             | aaa-028116     |

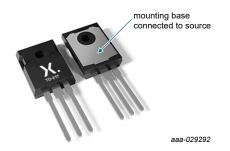

The Nexperia GAN063-650WSA is packaged in a TO247 (SOT429) package with a source tab. The traditional TO-247 provides excellent heat transfer, and therefore excellent power-handling capability.

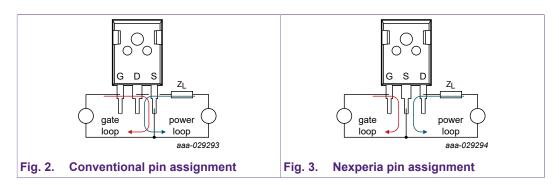

Note: the pin functions are different from a standard MOSFET: pin 1 is the gate, pin 2 is the source and pin 3 is the drain.

Using pin 2 as the source pin allows the circuit designer to keep the gate loop and the power loop separate. This facilitates a very clean design and greatly reduces or eliminates cross coupling. The PCB design can be optimised to take advantage of this feature.

## 4. Two-chip, integrated, normally-off power switch

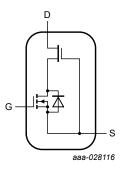

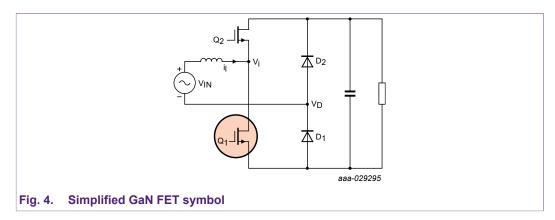

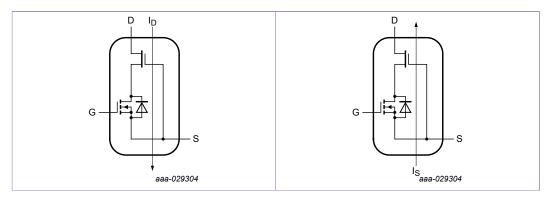

The full graphic symbol of a GaN FET is shown in the pinning information section of the data sheet. Note that the symbol includes two devices:

- Low-voltage Si MOSFET with a p-n body diode

- High-voltage GaN FET without a p-n body diode

The full graphic symbol shows that the device is a two chip integrated switch. Functionally the switch is normally off. Internally the device is built with two chips. The high-voltage GaN HEMT or FET is normally on, which is the type most naturally made with GaN, and is combined with a high performance normally-off Si MOSFET specifically developed to complement the GaN HEMT. The two chips are integrated with absolute minimum inductance between them.

In circuit schematics where just the basic switching function is important, a simple N-channel FET symbol is used to represent the complete, integrated switch (see Q1 circled in red above). When you see the simple symbol, understand that it represents this two-chip integrated combination.

## 5. GaN FET limiting values

The limiting values table provides the range of operating conditions allowed for the GaN FET. The conditions are defined in accordance with the *Absolute Maximum Rating System (IEC 60134)*.

Operation outside of these conditions is not guaranteed, so it is recommended that these values are never exceeded. Doing so risks immediate device failure or reduced lifetime of the GaN FET. To calculate how the limiting values change with temperature de-rating curves are provided.

The limiting values table for the GAN063-650WSA is given as an example of a standard limiting values table, in <u>Table 2</u>.

#### Table 2. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                         | Conditions                                               | Min | Max  | Unit |

|---------------------|-----------------------------------|----------------------------------------------------------|-----|------|------|

| V <sub>DS</sub>     | drain-source voltage              | -55 °C ≤  T <sub>j</sub> ≤  175 °C                       | -   | 650  | V    |

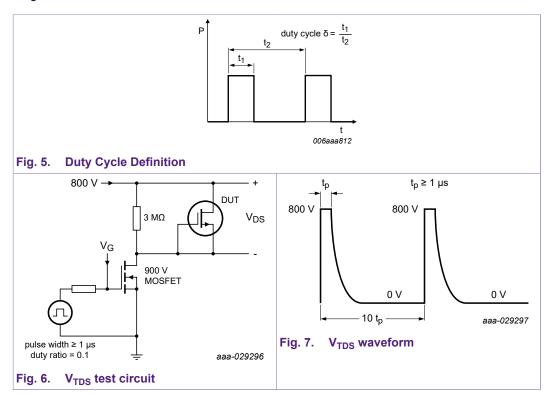

| V <sub>TDS</sub>    | transient drain to source voltage | pulsed; $t_p = 1 \ \mu s$ ; $\delta_{factor} = 0.01$     | -   | 800  | V    |

| V <sub>GS</sub>     | gate-source voltage               |                                                          | -20 | 20   | V    |

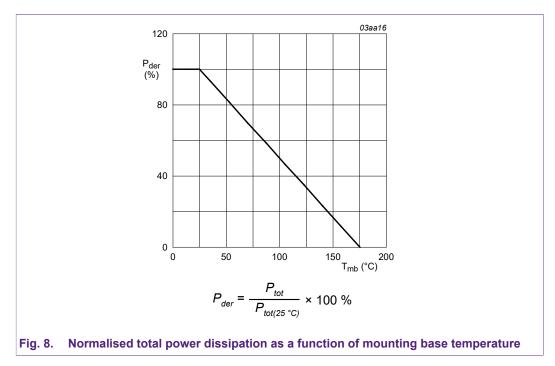

| P <sub>tot</sub>    | total power dissipation           | T <sub>mb</sub> = 25 °C; <u>Fig. 8</u>                   | -   | 143  | W    |

| I <sub>D</sub>      | drain current                     | V <sub>GS</sub> = 10 V; T <sub>mb</sub> = 25 °C          | -   | 34.5 | А    |

|                     |                                   | V <sub>GS</sub> = 10 V; T <sub>mb</sub> = 100 °C         | -   | 24.4 | А    |

| I <sub>DM</sub>     | peak drain current                | pulsed; $t_p \le 10 \ \mu s$ ; $T_{mb} = 25 \ ^{\circ}C$ | -   | 150  | А    |

| T <sub>stg</sub>    | storage temperature               |                                                          | -55 | 150  | °C   |

| Tj                  | junction temperature              |                                                          | -55 | 175  | °C   |

| T <sub>sld(M)</sub> | peak soldering<br>temperature     |                                                          | -   | 260  | °C   |

| Source-drai         | n diode                           |                                                          |     | 1    |      |

| I <sub>S</sub>      | source current                    | T <sub>mb</sub> = 25 °C; V <sub>GS</sub> = 0 V           | -   | 34.5 | А    |

| I <sub>SM</sub>     | peak source current               | pulsed; $t_p \le 10 \ \mu s$ ; $T_{mb} = 25 \ ^{\circ}C$ | -   | 150  | А    |

## 5.1. Drain-source voltage, V<sub>DS</sub>

| Table 4. Limit<br>In accordance | <b>ting values</b><br>e with the Absolute Maximum F | Rating System (IEC 60134).                           |     |     |      |

|---------------------------------|-----------------------------------------------------|------------------------------------------------------|-----|-----|------|

| Symbol                          | Parameter                                           | Conditions                                           | Min | Max | Unit |

| V <sub>DS</sub>                 | drain-source voltage                                | $-55 \ ^{\circ}C \le T_{j} \le 175 \ ^{\circ}C$      | -   | 650 | V    |

| V <sub>TDS</sub>                | transient drain to source voltage                   | pulsed; $t_p = 1 \ \mu s$ ; $\delta_{factor} = 0.01$ | -   | 800 | V    |

This 650 V rating is the maximum value that will give you the desired product life.

GaN FETs do not have an avalanche breakdown mechanism. The Nexperia GaN FET does not typically show any significant leakage current until a  $V_{DS}$  well beyond 800 V is reached. So there is an extra margin in  $V_{DS}$  before excess leakage occurs. If the GaN FET is subjected to a sufficiently high voltage, well beyond the specified maximum, then because there is no clamping mechanism damage and failure will occur. Since GaN FETs do not have an avalanche breakdown mechanism they are immune to cosmic radiation and so no further derating is required.

- V<sub>DS</sub> is the maximum voltage the device is guaranteed to block between drain and source terminals in the off-state. V<sub>DS</sub> is a DC rating

- $V_{DS}$  is not limited by avalanche breakdown; the rating can be applied over the entire operating range of -55 °C to 175 °C in contrast to the  $V_{DS}$  for a Si MOSFET which must be de-rated below 25 °C

| Table 4. Limi<br>In accordance | <b>ting values</b><br>e with the Absolute Maximum F | Rating System (IEC 60134).                          |     |     |      |

|--------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----|-----|------|

| Symbol                         | Parameter                                           | Conditions                                          | Min | Max | Unit |

| V <sub>DS</sub>                | drain-source voltage                                | -55 °C ≤ T <sub>j</sub> ≤ 175 °C                    | -   | 650 | V    |

| V <sub>TDS</sub>               | transient drain to source voltage                   | pulsed; $t_p = 1 \ \mu s; \ \delta_{factor} = 0.01$ | -   | 800 | V    |

## 5.2. Transient drain-source voltage, V<sub>TDS</sub>

$V_{\text{TDS}}$  is the **Maximum** repetitive transient voltage the device is guaranteed to block between drain and source in the off state. This transient rating, applies over the entire operating temperature range.

|                  |                                   | Rating System (IEC 60134).                     |     |     |      |

|------------------|-----------------------------------|------------------------------------------------|-----|-----|------|

| Symbol           | Parameter                         | Conditions                                     | Min | Max | Unit |

| V <sub>DS</sub>  | drain-source voltage              | -55 °C ≤ T <sub>j</sub> ≤ 175 °C               | -   | 650 | V    |

| V <sub>TDS</sub> | transient drain to source voltage | pulsed; $t_p$ = 1 µs; $\delta_{factor}$ = 0.01 | -   | 800 | V    |

| V <sub>GS</sub>  | gate-source voltage               |                                                | -20 | 20  | V    |

| P <sub>tot</sub> | total power dissipation           | T <sub>mb</sub> = 25 °C                        | -   | 143 | W    |

## 5.3. Gate source voltage, V<sub>GS</sub> and total power dissipation, P<sub>tot</sub>

## $\mathbf{V}_{\text{GS}}$

Maximum voltage the device is guaranteed to block between the gate and source terminals. This is a <u>DC rating</u>, and applies over the entire operating temperature range.

### $\mathbf{P}_{tot}$

$\mathsf{P}_{tot}$  is the Total Power dissipation is the maximum for a device with a mounting base temperature of 25 °C.

Power dissipation is calculated as that which would take the device to the maximum allowed junction temperature while keeping the mounting base at 25 °C.

| Symbol              | Parameter                         | Conditions                                              | Min | Max  | Unit |

|---------------------|-----------------------------------|---------------------------------------------------------|-----|------|------|

| V <sub>DS</sub>     | drain-source voltage              | -55 °C ≤ T <sub>j</sub> ≤ 175 °C                        | -   | 650  | V    |

| V <sub>TDS</sub>    | transient drain to source voltage | pulsed; $t_p$ = 1 µs; $\delta_{factor}$ = 0.01          | -   | 800  | V    |

| V <sub>GS</sub>     | gate-source voltage               |                                                         | -20 | 20   | V    |

| P <sub>tot</sub>    | total power dissipation           | T <sub>mb</sub> = 25 °C                                 | -   | 143  | W    |

| ID                  | drain current                     | V <sub>GS</sub> = 10 V; T <sub>mb</sub> = 25 °C         | -   | 34.5 | A    |

|                     |                                   | V <sub>GS</sub> = 10 V; T <sub>mb</sub> = 100 °C        | -   | 24.4 | A    |

| I <sub>DM</sub>     | peak drain current                | pulsed; $t_p \le 10 \ \mu s$ ; $T_{mb} = 25 \ ^\circ C$ | -   | 150  | A    |

| T <sub>stg</sub>    | storage temperature               |                                                         | -55 | 175  | °C   |

| Tj                  | junction temperature              |                                                         | -55 | 175  | °C   |

| T <sub>sld(M)</sub> | peak soldering temperature        |                                                         | -   | 260  | °C   |

| Source-drai         | n diode                           |                                                         |     |      |      |

| Is                  | source current                    | T <sub>mb</sub> = 25 °C; V <sub>GS</sub> = 0 V          | -   | 34.5 | A    |

| I <sub>SM</sub>     | peak source current               | pulsed; t <sub>p</sub> ≤ 10 µs; T <sub>mb</sub> = 25 °C | -   | 150  | A    |

## 5.4. Continuous and pulsed currents, $I_{\text{D}},\,I_{\text{DM}},\,I_{\text{S}}$ and $I_{\text{SM}},$

The 25 °C current ratings are the same for both current directions ( $I_D$  and  $I_S$ ).

The maximum current at any  $T_{mb}$  is the current which increases  $T_j$  to the maximum allowed temperature (175  $^\circ C).$

AN90005

# 6. GaN FET static characteristics

These are the device parameters that explain how the GaN FET behaves in it normal operating conditions

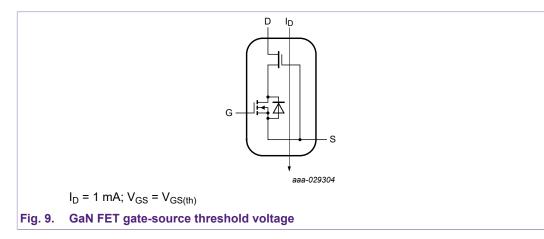

## 6.1. Gate-source threshold voltage, V<sub>GS(th)</sub>

| Symbol              | Parameter             | Conditions                                                                         | Min | Тур | Max | Unit |

|---------------------|-----------------------|------------------------------------------------------------------------------------|-----|-----|-----|------|

| Static chara        | acteristics           | · · · · · ·                                                                        |     |     |     |      |

| V <sub>GS(th)</sub> | gate-source threshold | $I_D = 1 \text{ mA}; V_{DS}=V_{GS}; T_j = 25 \text{ °C}$                           | 3.5 | 3.9 | 4.4 | V    |

|                     | voltage               | I <sub>D</sub> = 1 mA; V <sub>DS</sub> =V <sub>GS</sub> ; T <sub>j</sub> = 175 °C. | 2.3 | -   | -   | V    |

|                     |                       | $I_D = 1 \text{ mA}; V_{DS}=V_{GS}; T_j = -55 \text{ °C}$                          | -   | -   | 5   | V    |

| I <sub>DSS</sub>    | drain leakage current | $V_{DS} = 650 \text{ V}; V_{GS} = 0 \text{ V}; T_j = 25 \text{ °C}$                | -   | 2   | 25  | μA   |

|                     |                       | V <sub>DS</sub> = 650 V; V <sub>GS</sub> = 0 V; T <sub>j</sub> = 175 °C            | -   | 25  | -   | μA   |

| I <sub>GSS</sub>    | gate leakage current  | V <sub>GS</sub> = -20 V; V <sub>DS</sub> = 0 V; T <sub>j</sub> = 25 °C             | -   | 10  | 100 | nA   |

|                     |                       | V <sub>GS</sub> = 20 V; V <sub>DS</sub> = 0 V; T <sub>j</sub> = 25 °C              | -   | 10  | 100 | nA   |

Gate-source threshold voltage for the GaN FET device is the gate-source threshold voltage of the Si MOSFET. This gate threshold is 3.9 V typically, with a negative temperature co-efficient.

| Doon | aiatanaa | $V_{GS} = 10 \text{ V}; I_D = 25 \text{ A}; T_j = 25 ^{\circ}\text{C}$<br>$V_{GS} = 10 \text{ V}; I_D = 25 \text{ A}; T_j = 175 ^{\circ}\text{C}$ |  | - | 50<br>120 | 60<br>- | mΩ<br>mΩ |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|---|-----------|---------|----------|

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|---|-----------|---------|----------|

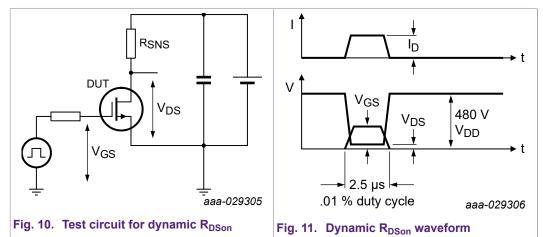

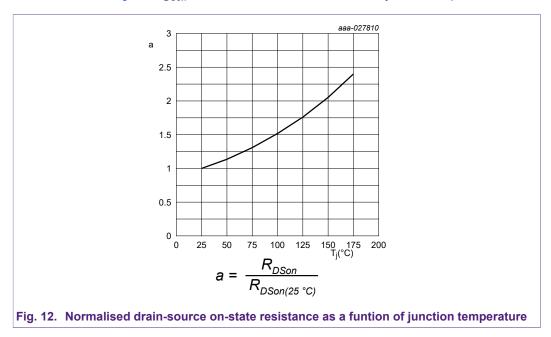

### 6.2. Drain-source on-state resistance, R<sub>DSon</sub>

$R_{DSon}$  is the drain-to-source on-state resistance of the GaN FET. This has a dynamic value for GaN FETs. When  $R_{DSon}$  is measured immediately after turn-on, following period of blocking high-voltage, this value will be slightly higher than normal. This is due to temporary charge trapping in the device structure. Nexperia have optimised the device so that charge trapping and dynamic  $R_{DSon}$  are minimised.

As can be seen in Fig. 12,  $R_{DSon}$  is shown as a normalised function of junction temperature.

# 7. GaN FET dynamic characteristics

These are the device parameters that explain how the GaN FET behaves in its normal operating conditions

## 7.1. Gate charge $Q_{G(tot)}$ , $Q_{GS}$ and $Q_{GD}$

| Dynamic characteristics |                    |                                                                      |  |   |    |   |    |

|-------------------------|--------------------|----------------------------------------------------------------------|--|---|----|---|----|

| Q <sub>G(tot)</sub>     | total gate charge  | $I_D = 25 \text{ A}; V_{DS} = 400 \text{ V}; V_{GS} = 10 \text{ V};$ |  | - | 15 | - | nC |

| Q <sub>GS</sub>         | gate-source charge | T <sub>j</sub> = 25 °C                                               |  | - | 6  | - | nC |

| Q <sub>GD</sub>         | gate-drain charge  |                                                                      |  | - | 4  | - | nC |

Gate charge for GaN FET is defined in the same way as a normal MOSFET, because the cascode arrangement of a GaN FET means that the gate is in fact the gate of a LV MOSFET. Since the LV MOSFET is a relatively small device it has a small gate charge suited to high speed switching.

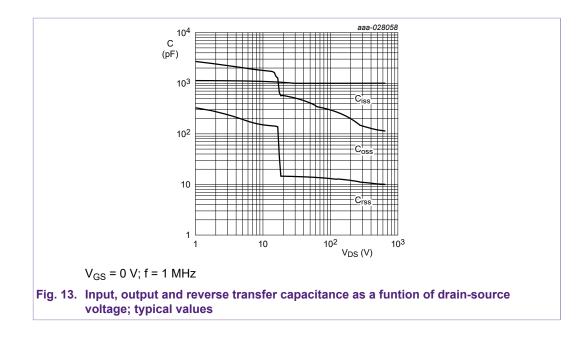

## 7.2. Capacitances $C_{iss}$ , $C_{oss}$ and $C_{rss}$

| C <sub>iss</sub> | input capacitance               | V <sub>DS</sub> = 400 V; V <sub>GS</sub> = 0 V; f = 1 MHz; | - | 1000 | - | pF |

|------------------|---------------------------------|------------------------------------------------------------|---|------|---|----|

| C <sub>oss</sub> | output capacitance              | T <sub>j</sub> = 25 °C                                     | - | 130  | - | pF |

| C <sub>rss</sub> | reverse transfer<br>capacitance |                                                            | - | 8    | - | pF |

Traditional small signal capacitance is shown in <u>Fig. 13</u>. The discontinuity (step change) in <u>Fig. 13</u> is where GaN HEMT pinches off. Capacitance relates charge to voltage and energy to voltage. For a linear capacitance, the following fundamental equations apply:

$$Q = CV E = \frac{CV^2}{2}$$

The capacitances  $C_{o\left(er\right)}$  and  $C_{o\left(tr\right)}$  attempt to capture these relationships for a nonlinear capacitance.

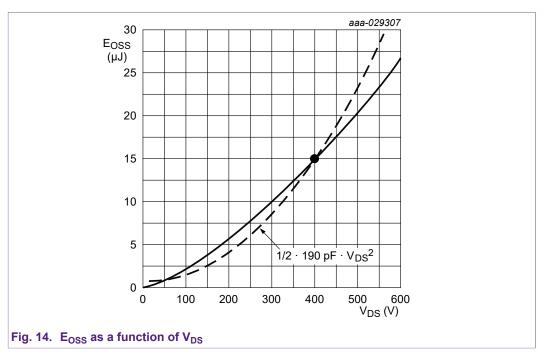

## 7.3. Effective output capacitance (energy related), Co(er)

| C <sub>o(er)</sub> | effective output<br>capacitance, energy<br>related | $\begin{array}{l} 0 \ V \leq \ V_{DS} \leq \ 400 \ V; \ V_{GS} = 0 \ V; \\ T_{j} = 25 \ ^{\circ}C \end{array}$ | - | 190 | - | pF |

|--------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---|-----|---|----|

| C <sub>o(tr)</sub> | effective output<br>capacitance, time<br>related   | $0 V \le V_{DS} \le 400 V; V_{GS} = 0 V;$<br>T <sub>j</sub> = 25 °C                                            | - | 310 | - | pF |

The GaN FET capacitance parameter  $C_{o(er)}$  is the effective output capacitance (energy-related) dependent on the drain voltage

Note that  $0 \le V_{DS} \le 400$  V shown above, means as the voltage rises from 0 V to 400 V.

$$E_{\rm oss} = \int_{0}^{Q_{\rm oss}} V_{\rm DS} \cdot dq = \int_{0}^{V} V_{\rm DS} \cdot C \left( V_{\rm DS} \right) \cdot dV_{\rm DS}$$

At a specific  $V_{\text{DS}},$  a unique value of  $C_{\text{oss}}$  satisfies the equation:

$$E_{\rm oss} = 1/2 \cdot \rm Co(er) \cdot V_{\rm DS}^2$$

e.g.

$$E_{\rm oss} = 1/2 \cdot 190 \rm{pF} \cdot 400^2 = 15.2 \mu$$

By integrating  $C_{OSS}$  with respect to  $V_{DS}$ , the result will be  $Q_{OSS}$ . If we then integrate  $Q_{OSS}$  with respect to  $V_{DS}$ , we will then arrive at  $E_{OSS}$ .

E<sub>OSS</sub> \* switching frequency will give the switching power loss in Watts.

| $C_{\text{o}(\text{er})}$ | effective output<br>capacitance, energy<br>related | $\begin{array}{l} 0 \; V \leq \; V_{\text{DS}} \leq \; 400 \; \text{V}; \; V_{\text{GS}} = 0 \; \text{V}; \\ T_{j} = 25 \; ^{\circ}\text{C} \end{array}$ | - | 190 | - | pF |

|---------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|----|

| C <sub>o(tr)</sub>        | effective output<br>capacitance, time<br>related   | $0 V \le V_{DS} \le 400 V$ ; $V_{GS} = 0 V$ ;<br>$T_j = 25 \ ^{\circ}C$                                                                                  | - | 310 | - | pF |

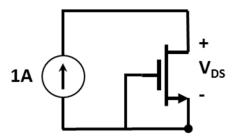

## 7.4. Effective output capacitance (time related), $C_{o(tr)}$

The GaN FET capacitance parameter  $C_{o(tr)}$  is the equivalent capacitance to give same charging time, as  $V_{DS}$  rises from 0 V to 400 V. This can also be described as a constant current being used to charge the output capacitance, giving a time related effective value.

$$Q_{\rm oss} = \int_{0}^{Q_{\rm oss}} dq = \int_{0}^{V} C \left( V_{\rm DS} \right) \cdot dV_{\rm DS}$$

At a specific  $V_{\text{DS}},$  a unique value of  $C_{\text{oss}}$  satisfies the equation:

$$V_{\rm ds} = \frac{Q_{\rm oss}}{C_{\rm (tr)}} = \frac{1}{C_{\rm o(tr)}} \int_{0}^{t} i(t) \cdot dt$$

e.g.

$$400V = \frac{1}{310 \text{pF}} \cdot \int_{0}^{120 \text{ns}} 1.0A \cdot \text{dt}$$

$$Q_{\text{oss}} = 124nC$$

AN90005

© Nexperia B.V. 2020. All rights reserved

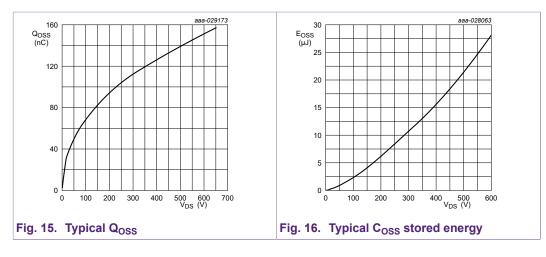

### 7.5. Output charge and stored energy, $Q_{oss}$ and $E_{oss}$

Rather than using the  $C_{o(tr)}$  and  $C_{o(er)}$  parameters, it is much easier to use the graphs shown below that are also available in the data sheet. The respective  $Q_{OSS}$  and  $E_{OSS}$  values can be read directly for the required  $V_{DS}$ .

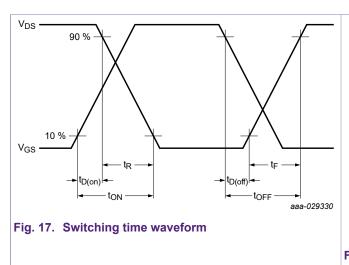

### 7.6. GaN FET switching time characteristics

| t <sub>d(on)</sub>  | turn-on delay time  | $V_{DS} = 400 \text{ V}; \text{ R}_{L} = 16 \Omega; \text{ V}_{GS} = 12 \text{ V};$ | - | 55 | - | ns |

|---------------------|---------------------|-------------------------------------------------------------------------------------|---|----|---|----|

| t <sub>r</sub>      | rise time           | $R_{G(ext)} = 40 \Omega$                                                            | - | 10 | - | ns |

| t <sub>d(off)</sub> | turn-off delay time |                                                                                     | - | 88 | - | ns |

| t <sub>f</sub>      | fall time           |                                                                                     | - | 11 | - | ns |

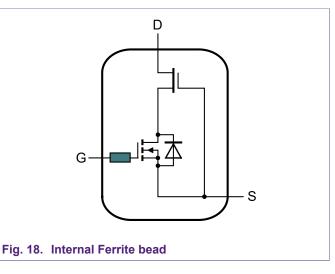

Nexperia GaN FETs generally require a ferrite bead in series with the gate. This serves to de-"Q" the gate-source loop and improve the switching stability. The ferrite bead effectively provides damping impedance at frequencies > 100 MHz. It also introduces a small propagation delay, however it does not introduce any additional loss.

The GAN063-650WSA in TO247 package has an integral ferrite bead, and so an external bead is not required. Newer GaN FETs may not include the integral ferrite bead, and so one must be included in the external gate drive. Always refer to the data sheet of specific devices for details.

| Source-drain diode |                       |                                                          |   |      |   |    |  |

|--------------------|-----------------------|----------------------------------------------------------|---|------|---|----|--|

| V <sub>SD</sub>    | source-drain voltage  | $I_{S}$ = 25 A; $V_{GS}$ = 0 V; $T_{j}$ = 25 °C.         | - | 1.9  | - | V  |  |

|                    |                       | $I_{S}$ = 12.5 A; $V_{GS}$ = 0 V; $T_{j}$ = 25 °C        | - | 1.35 | - | V  |  |

| t <sub>rr</sub>    | reverse recovery time | I <sub>S</sub> = 25 A; dI <sub>S</sub> /dt = -1000 A/μs; | - | 54   | - | ns |  |

| Qr                 | recovered charge      | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 400 V           | - | 125  | - | nC |  |

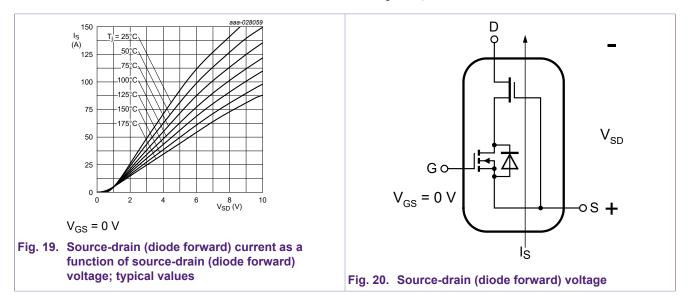

### 7.7. Source-drain voltage, V<sub>SD</sub>

This device parameter source-drain voltage refers to the GaN FET device when it is acting as a two terminal device when not enhanced with the gate  $V_{GS} = 0$  V.

$V_{SD}$  is the voltage developed whilst GaN FET conducts in reverse direction (e.g. acting as a rectifier carrying freewheeling current) Here the voltage  $V_{SD}$  comprises the forward voltage of the Silicon MOSFET body diode and the voltage drop across the 2 DEG channel of the GaN HEMT.

## 8. Q<sub>r</sub> for GaN FET switches

| Dynamic c           | haracteristics        |                                                                         |   |      |    |    |

|---------------------|-----------------------|-------------------------------------------------------------------------|---|------|----|----|

| Q <sub>G(tot)</sub> | total gate charge     | I <sub>D</sub> = 25 A; V <sub>DS</sub> = 400 V; V <sub>GS</sub> = 10 V; | - | 15   | -  | nC |

| Q <sub>GS</sub>     | gate-source charge    | T <sub>j</sub> = 25 °C                                                  | - | 6    | -  | nC |

| Q <sub>GD</sub>     | gate-drain charge     |                                                                         | - | 4    | -  | nC |

| Q <sub>oss</sub>    | output charge         | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 400 V                          | - | 125  | )  | nC |

| Source-dra          | ain diode             | · · ·                                                                   |   |      |    |    |

| V <sub>SD</sub>     | source-drain voltage  | I <sub>S</sub> = 25 A; V <sub>GS</sub> = 0 V; T <sub>j</sub> = 25 °C    | - | 1.9  | -  | V  |

|                     |                       | I <sub>S</sub> = 12.5 A; V <sub>GS</sub> = 0 V; T <sub>j</sub> = 25 °C  | - | 1.35 | -  | V  |

| t <sub>rr</sub>     | reverse recovery time | I <sub>S</sub> = 25 A; dI <sub>S</sub> /dt = -1000 A/μs;                | - | 54   | -  | ns |

| Q <sub>r</sub>      | recovered charge      | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 400 V                          | - | 125  | )- | nC |

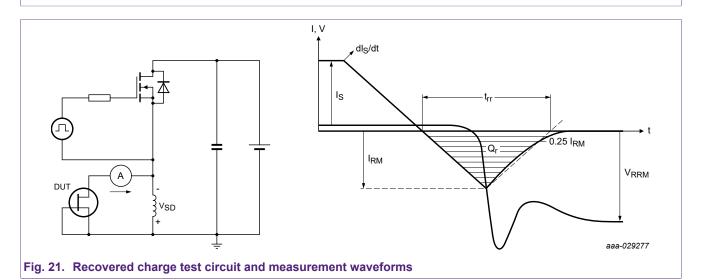

The Device Under Test (DUT) is carrying a freewheeling current. The switch in the high side of the test circuit in Fig. 21 will then turn on and force a transition at the switching node from low voltage to high voltage. This will cause the current in the DUT to change from freewheeling current to some negative current up until the point that the DUT is blocking the full DC supply voltage. If you integrate the negative current you will get the minority carrier stored change plus any output capacitance charge.

For GaN FETs, the charge on the output capacitance  $Q_{OSS}$  is the dominant component of the reverse recovery charge  $Q_r$ . Hence the reason that the datasheet for the Nexperia GaN FET specifies the same value for both  $Q_{OSS}$  and  $Q_r$ .

Some GaN device manufacturers will claim to have zero reverse recovery charge Qr because they do not have a PN junction body diode. However, they will still have  $Q_{OSS}$ .

AN90005

## 9. Switching-node snubber

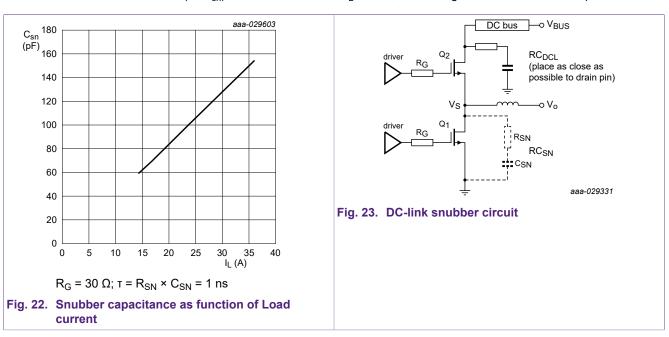

To achieve maximum efficiency and stability when switching high currents, a switching node RC snubber (R,  $C_{sn}$ ) is recommended. For  $I_1 < 14$  A, a switching-node snubber is not required.

**Note:** a DC-link snubber is recommended in all cases. Optimal is 20 nF in series with 4  $\Omega$ , most easily achieved with parallel combination 10 nF and 8  $\Omega$ . This snubber lowers the Q factor of any resonance in the bus. That resonance will act as a load on the high gain amplifier that is the GaN FET and can lead to instability.

For some GaN FETs, like the GAN063-650WSA, an RC snubber is recommended for the switching node. This will increase switching loss, so this is only recommended at high power levels where the losses are a very small percentage of the total power. Other GaN FETs do not require a snubber on the switching node at any power level. **Always refer to the data sheet of specific devices for details**.

## 10. Revision history

| Table 3. Revision history |            |                                                |  |  |  |  |

|---------------------------|------------|------------------------------------------------|--|--|--|--|

| Revision<br>number        | Date       | Description                                    |  |  |  |  |

| 2.0                       | 2020-06-08 | Section 5.1, Section 7.6 and Section 9 updated |  |  |  |  |

| 1.1                       | 2019-02-13 | Initial version                                |  |  |  |  |

| 1.0                       | 2018-11-09 | Preliminary version                            |  |  |  |  |

# 11. Legal information

#### Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer's third party customer's hird party customer's. Nexperia does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

# **List of Tables**

| Table 1. Pinning information | 2 |

|------------------------------|---|

| Table 2. Limiting values     | 4 |

| Table 3. Revision history1   | 6 |

AN90005

# List of Figures

| Fig. 1. GaN FET Nomenclature2                                                                                       |

|---------------------------------------------------------------------------------------------------------------------|

| Fig. 2. Conventional pin assignment3                                                                                |

| Fig. 3. Nexperia pin assignment                                                                                     |

| Fig. 4. Simplified GaN FET symbol3                                                                                  |

| Fig. 5. Duty Cycle Definition5                                                                                      |

| Fig. 6. VTDS test circuit5                                                                                          |

| Fig. 7. VTDS waveform5                                                                                              |

| Fig. 8. Normalised total power dissipation as a function of mounting base temperature                               |

| Fig. 9. GaN FET gate-source threshold voltage8                                                                      |

| Fig. 10. Test circuit for dynamic RDSon9                                                                            |

| Fig. 11. Dynamic RDSon waveform9                                                                                    |

| Fig. 12. Normalised drain-source on-state resistance as a funtion of junction temperature9                          |

| Fig. 13. Input, output and reverse transfer capacitance as a funtion of drain-source voltage; typical values        |

| Fig. 14. EOSS as a function of VDS11                                                                                |

| Fig. 15. Typical QOSS 13                                                                                            |

| Fig. 16. Typical COSS stored energy 13                                                                              |

| Fig. 17. Switching time waveform                                                                                    |

| Fig. 18. Internal Ferrite bead 13                                                                                   |

| Fig. 19. Source-drain (diode forward) current as a function of source-drain (diode forward) voltage; typical values |

| Fig. 20. Source-drain (diode forward) voltage14                                                                     |

| Fig. 21. Recovered charge test circuit and measurement waveforms                                                    |

| Fig. 22. Snubber capacitance as function of Load current. 16                                                        |

| Fig. 23. DC-link snubber circuit16                                                                                  |

|                                                                                                                     |

# Contents

| 1. I | Introduction                                                                      | 2    |

|------|-----------------------------------------------------------------------------------|------|

| 2. I | Nomenclature                                                                      | 2    |

| 3. I | Pinning information                                                               | 2    |

| 4. T | 「wo-chip, integrated, normally-off power switch                                   | 3    |

| 5. ( | GaN FET limiting values                                                           | 4    |

| 5.1. | Drain-source voltage, V <sub>DS</sub>                                             | 4    |

| 5.2. | Transient drain-source voltage, V <sub>TDS</sub>                                  | 5    |

|      | Gate source voltage, V <sub>GS</sub> and total power<br>ipation, P <sub>tot</sub> | 6    |

| 5.4. | Continuous and pulsed currents, $I_{D},I_{DM},I_{S}$ and $I_{SM},.$               | 7    |

| 6. ( | GaN FET static characteristics                                                    | 8    |

| 6.1. | Gate-source threshold voltage, $V_{GS(th)}\!\!\!\!$                               | 8    |

| 6.2. | Drain-source on-state resistance, R <sub>DSon</sub>                               | 9    |

| 7. C | GaN FET dynamic characteristics                                                   | .10  |

| 7.1. | Gate charge $Q_{G(tot)}$ , $Q_{GS}$ and $Q_{GD}$                                  | 10   |

| 7.2. | Capacitances C <sub>iss</sub> , C <sub>oss</sub> and C <sub>rss</sub>             | . 10 |

| 7.3. | Effective output capacitance (energy related), $C_{o(er)}$                        | 11   |

| 7.4. | Effective output capacitance (time related), $C_{o(tr)}$                          | .12  |

| 7.5. | Output charge and stored energy, $Q_{\text{oss}}$ and $E_{\text{oss}}$            | . 13 |

| 7.6. | GaN FET switching time characteristics                                            | .13  |

| 7.7. | Source-drain voltage, V <sub>SD</sub>                                             | . 14 |

| 8. ( | Q <sub>r</sub> for GaN FET switches                                               | . 15 |

| 9. 3 | Switching-node snubber                                                            | .16  |

| 10.  | Revision history                                                                  | .16  |

| 11.  | Legal information                                                                 | .17  |

© Nexperia B.V. 2020. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 8 June 2020